ACS APPLIED MATERIALS

# Self-Induced Gate Dielectric for Graphene Field-Effect Transistor

Kaliannan Thiyagarajan, Balasubramaniam Saravanakumar, Rajneesh Mohan, and Sang-Jae Kim\*

Nanomaterials and System Lab, Department of Mechatronics Engineering, Jeju National University, Jeju 690-756, Republic of Korea

## Supporting Information

**ABSTRACT:** We report the electronic characteristics of an avant-garde graphene-field-effect transistor (G-FETs) based on ZnO microwire as topgate electrode with self-induced dielectric layer. Surface-adsorbed oxygen is wrapped up the ZnO microwire to provide high electrostatic gate-channel capacitance. This nonconventional device structure yields an on-current of 175  $\mu$ A, on/off current ratio of 55, and a device mobility exceeding 1630 cm<sup>2</sup>/(V s) for holes and 1240 cm<sup>2</sup>/(V s) for electrons at room temperature. Self-induced gate dielectric process prevents G-FETs from impurity doping and defect formation in graphene lattice and facilitates the lithographic process. Performance degradation of G-FETs can be overcome by this avant-garde device structure.

KEYWORDS: graphene, field effect transistors, ZnO microwire, self-induced, surface oxygen

A single paper of graphite ignites a revolution in electronics<sup>1</sup> because of its two-dimensional structure and a linear energy dispersion relation, leading to potential application in nanoscale devices.<sup>2</sup> Graphene-based field-effect devices play an immense role in exploring the electronic properties of graphene.<sup>3</sup> Different gate architectures (back, top, and side gate) of graphene field-effect transistors (G-FETs) have their own merits and demerits. Gate oxide layer (dielectric) is an essential part of a transistor compare to the graphene channel. Optical visualization of graphene required 300 nm of SiO<sub>2</sub> capping layer over the back gate limits device performance.<sup>3–7</sup> Side-gated graphene FETs does not require any gate dielectric, which degrades the channel mobility. Hahnlein et al. reported high transconductance of G-FETs based on side-gate configuration.<sup>8</sup> At the same time transconductance and current–voltage (I-V)characteristics studies of side-gate-FETs are inadequate. As compared to back-gate and side-gate configurations, top-gated graphene FETs (TG-FETs) have the authorized control over the electronic properties of graphene channel,<sup>9</sup> which is due to the freedom of altering the dielectric material and its thickness.

The performance of TG-FET device is mainly dependent on the gate dielectric materials (high dielectric constant (k)) such as HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and ZrO<sub>2</sub>.<sup>10,11</sup> Depositing a high-quality gate dielectric without introducing defects on graphene lattice is a challenging task in the transistor fabrication process.<sup>12</sup> Although, atomic-layer deposition (ALD) is the common technique to deposit high-k dielectrics, which requires a initial functionalization process prior to the deposition. This results in the breaking of the chemical bond, defective structure, and even doping of unwanted impurities on graphene lattice, which can significantly affect the device mobility, on/off ratio, conductance, and subthreshold swing, and may also increase the noise level of G-FETs.<sup>12–14</sup> To overcome this performance degradation of graphene device, Liao et al. developed a concept of self-aligned gate electrodes based on Co<sub>2</sub>Si–Al<sub>2</sub>O<sub>3</sub> core– shell nanowire as a gate electrode.<sup>15</sup> The self-aligning method simplifies the lithographic process and minimizes the capacitance overlap. In this letter, we report a new type of G-FET device based on ZnO microwire as a top-gate electrode with self-induced dielectric layer. Surface-adsorbed<sup>16</sup> oxide layer of ZnO act as dielectric layer in this study. The high-*k* value of ZnO provides enough capacitance to control the active graphene channel.

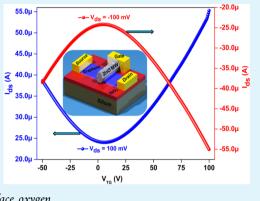

Figure 1a shows a schematic of the graphene/ZnO micro wire hybrid device. Graphene was prepared from highly oriented pyrolytic graphite (HOPG) by the micromechanical cleavage method and transferred onto SiO<sub>2</sub> (300 nm)/Si substrate and silver (paste) electrodes were made on both sides of graphene. ZnO microwires with diameters of  $\sim 5 \ \mu m$  and lengths of 20–150  $\mu$ m have been chosen and cautiously placed (vertically) over the graphene layer without damaging the crystal lattice. ZnO microwires were synthesized through thermal vapor-phase transport process for detail growth mechanism (see the Supporting Information, Experimental Section). The devices were heated on a hot plate for 150 °C to remove the surface-adsorbed oxygen; silver contacts were made on both sides of the hot microwire. The device was cooled to room temperature to readsorb the oxygen on the remaining parts of the ZnO microwire, making it insulating, and the wire underneath the silver contact remains more conducting than the rest of the wire. A field-emission scanning electron microscopy (FESEM) image of the fabricated self-induced

```

Received:

April 5, 2013

Accepted:

June 28, 2013

Published:

June 28, 2013

```

ACS Publications © 2013 American Chemical Society

6443

Figure 1. (a) Schematic of graphene FET device with ZnO microwire as a self-induced top-gate electrode, (b) typical FE-SEM image of self-induced top-gated graphene-FET (STG-FET).

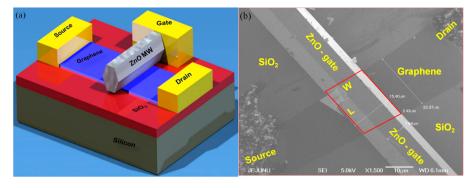

top-gated (ZnO microwire) graphene-FET (STG-FET) is shown in Figure 1b. After the fabrication of STG-FETs, Raman spectroscopy measurement was done with 514 nm Ar<sup>+</sup> ion laser as an excitation light source using Horiba Jobin Yvon LabRAM HR800 system. Raman spectrum of ZnO microwire is illustrated in Figure 2a and manifests the material quality and

Figure 2. Raman spectrum of (a) ZnO microwire and (b) single-layer graphene. Inset shows the optical microscopy image of a STG-FET device.

wurtzite crystal structure of the synthesized ZnO microwire. Zone center optical phonon modes for the Wurtzite crystal structure of ZnO microwire are A1+2B1+E1+2E2.17 Group theory predicts that the two B1 modes are Raman inactive and all the other modes are first-order Raman-active. The heavier Zn sublattice with nonpolar vibrations is the reason for the lowfrequency E<sub>2</sub> mode. The high-frequency E<sub>2</sub> mode predominantly involves the oxygen atoms. The second-order Raman peak at 331 cm<sup>-1</sup> is attributed to the acoustic phonons.<sup>18</sup> The two peaks at 379 and 410 cm<sup>-1</sup> in the spectrum correspond to  $A_1$  (TO) and  $E_1$  (TO) modes, respectively. The peaks corresponding to the LO modes are not present in the obtained spectrum. The peaks at 100 and 437  $cm^{-1}$  are associated with the two nonpolar Raman-active 2E2 (low and high) modes.<sup>19</sup> The line width of the  $E_2$  (high) mode is about 7.5 cm<sup>-1</sup>, whereas the line width of  $E_2$  (low) is about 2.4 cm<sup>-1</sup>. The corresponding peaks and line width values of the Raman spectrum confirm that the top-gated material is ZnO microwire.

Figure 2b shows the Raman spectrum of single layer graphene. Absence of D peak (defect) reveals the material quality. The full width at half-maximum (fwhm) of 2D peak is  $\sim$ 22 cm<sup>-1</sup> and the intensity ratio between 2D and G peaks is 2.9 these values indicates that, the STG-FET device was successfully fabricated on SiO<sub>2</sub>/Si substrate without causing any material damage. The inset in Figure 2 is the optical microscopy image of the fabricated STG-FET device. ZnO microwire plays an immense role, which defines the channel length (with respect to the width of the graphene layer), diameter of the microwire sets channel width and also working as a top-gate electrode. The active channel width (W) and length (L) of the STG-FET device is showed in Figure 1b. The surface oxide or depletion layers of ZnO microwire is pretended as gate dielectrics. The electrical characteristics of the device were measured by Agilent, B1500 A semiconductor parameter analyzer.

Gate oxide or depletion layer thickness of the STG-FET can be approximated  $\mbox{by}^{20,21}$

$$t = \left(\frac{2\varepsilon_0 \varepsilon_{\rm ZnO} V}{e N_{\rm D}}\right)^{1/2} \tag{1}$$

Here  $\varepsilon_{\rm o}$  is the permittivity of free space,  $\varepsilon_{\rm ZnO}$  is the dielectric constant of the top-gated ZnO microwire and is ~8.7,<sup>20</sup> *e* is electron charge, *V* is applied potential with order of 1 V, and  $N_{\rm D}$  is the free electron carrier density and is ~1 × 10<sup>17</sup> cm<sup>-3</sup>. The thickness of the top-gate dielectric layer is approximated to be 98 nm. The top-gate capacitance ( $C_{\rm TG}$ ) of STG-FET is estimated to be  $C_{\rm TG}$  = 78 nF/cm<sup>2</sup>, corresponding to a relative dielectric constant of ~8.7 with dielectric layer thickness of ~98 nm for the ZnO microwire.

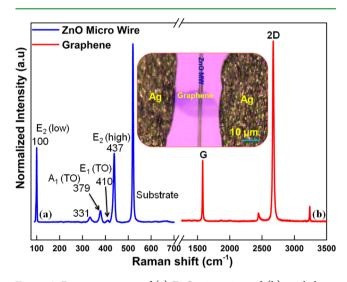

Electrical transport studies of fabricated STG-FET were carried out in ambient conditions. Self-aligned gate-dependent drain current ( $I_{\rm ds}$ ) versus drain voltage ( $V_{\rm ds}$ ) is shown in Figure 3a. The applied top-gate voltage was increased from -30 to 30 V with the step of 10 V. Figure 3a clearly shows that the gate voltage increases toward positive direction the device conductance decreases which is due to the influence of surface adsorbates.<sup>11,22</sup> In ambient conditions, the free charge carriers of ZnO microwire were depleted by the surface adsorbates. Consequently the electronic transport property of top-gated ZnO microwire is dominated by the injected electrons. Absorbance of O<sub>2</sub> from ambient condition form a depletion layer over the ZnO microwire surface with a thickness of ~98 nm reduces the carrier concentration of ZnO microwire.<sup>20,22</sup>

Top-gate voltage-induced carrier concentration is given by  $n = ((\varepsilon_0 \varepsilon_{0x} V_{TG})/(t_{0x} e))$ , where *e* is electron charge, and  $V_{GT}$  is a

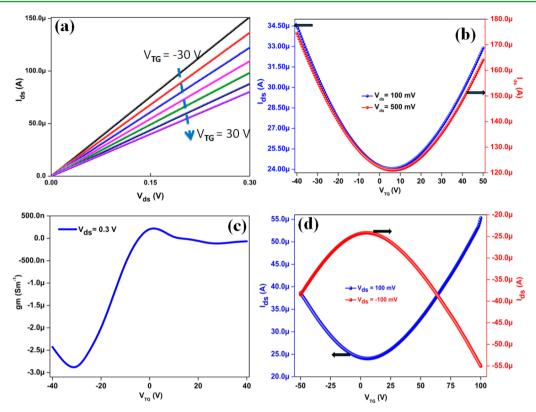

Figure 3. (a) Output characteristic ( $I_{ds}-V_{ds}$ ) of STG-FET recorded at different gate voltage from -30 to 30 V with the step of 10 V. (b) Transfer characteristics ( $I_{ds}-V_{TG}$ ) of STG-FET at the drain source voltage of 100 mV, 500 mV during the sweep of top-gate bias from -40 to 50 V. (c) Transconductance ( $g_m$ ) of STG-FET as a function of top-gate voltage at  $V_{ds}$  of 300 mV. (d) Transfer characteristics of STG-FET at two different channel bias voltage.

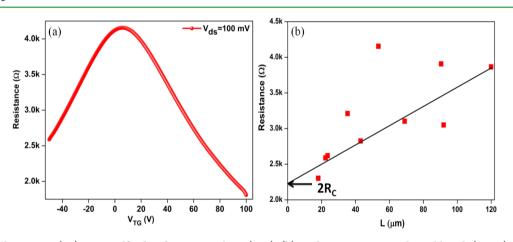

Figure 4. (a) Total resistance  $(R_T)$  versus self-induced top-gate voltage  $(V_{TG})$ , (b) total resistance versus channel length  $(R_T-L)$  plot of STG-FET devices.

top-gate voltage. For typical  $V_{\rm GT} = 50$  V, the formula yields  $n = 2.45 \times 10^{12}$  cm<sup>-2</sup> for the STG-FET device. The transfer characteristics of drain—source current ( $I_{\rm ds}$ ) vs self-induced top-gate voltage ( $V_{\rm TG}$ ) of the STG-FET device at  $V_{\rm ds} = 100$  and 500 mV is shown in Figure 3b. At  $V_{\rm TG} = 0$  V, the device shows p-channel operation and a perfect symmetric ambipolar behavior was observed with the Dirac point located at 5 V of gate voltage. We observed one order increment in drain current ( $I_{\rm ds}$ ) with respect to drain voltage ( $V_{\rm ds}$ ). The STG-FET device can delivers an on-current of 175  $\mu$ A at  $V_{\rm ds} = 500$  mV for  $V_{\rm TG} = -40$  V and the room temperature on/off current ratio of the device is 55 at  $V_{\rm ds} = 500$  mV.

Figure 3c represents the gate-dependent transconductance of STG-FET, which is defined as  $g_{\rm m} = dI_{\rm ds}/dV_{\rm TG}$  and the transconductance of the device significantly varied with respect to the applied gate potential. The peak transconductance values are found to be 275 nS for positive branch (n-type) and 2.9  $\mu$ S for negative branch (p-type) of  $V_{\rm TG}$ . The hole branch current is larger than electron branch current, which leads to high field effect mobility of 3588 cm<sup>2</sup>/(V s) for holes and 340 cm<sup>2</sup>/(V s) for electron (including the contact resistance). The mobility values are derived through transconductance method  $\mu_{\rm DEV} = ((g_{\rm m}L)/(V_{\rm D}WC_{\rm TG}))$ , here channel length *L* is 53.5  $\mu$ m, and channel width W is 5.5  $\mu$ m. This huge difference in device mobility arises because of the greater number of negative

### **ACS Applied Materials & Interfaces**

charges induced on ZnO microwire surface by the positive voltage, which leads to the increment in oxide layer thickness resulting in the reduction of transconductance. Figure 3d shows the transfer characteristics of STG-FET device at different channel bias. At different bias voltage, the device delivers the same amount of current. The minimum conductance is reproduced when applying the negative drain voltage. It suggests that the surface-induced oxide layer does not affect by the channel bias.

Figure 4a shows the resistance (*R*) as a function of top-gate voltage at  $V_{\rm ds} = 100$  mV. The maximum resistance reveals the charge neutrality point (Dirac point) of the device. To calculate the device mobility value, it is necessary to exclude the contact resistance that is comparable to the device channel resistance. Transfer length measurement (TLM) method has been used to measure contact resistance ( $R_{\rm C}$ ) of STG-FET with different channel length. Here the graphene channel width or diameter of the ZnO microwire is ~5  $\mu$ m. The total resistance ( $R_{\rm T}$ ), corresponding channel length (*L*) ( $R_{\rm T}-L$  plot) of the fabricated device is given in Figure 4b. The contact resistance of STG-FET device was extracted through a linear fit which intercept at L = 0, gives the total contact resistance  $2R_{\rm C} = 2.2$  K $\Omega$ . The total resistance of the STG-FET device can be expressed with the following relation<sup>23,24</sup>

$$R_{\text{total}} = 2R_{\text{C}} + R_{\text{channel}} = 2R_{\text{C}} + \frac{L}{We\mu\sqrt{(n_0^2 + n^2)}}$$

(2)

where  $R_{\text{total}}$  is the total resistance of the STG-FET device.  $R_{\text{C}}$  is the metal/graphene contact resistance.  $R_{\text{channel}}$  is the resistance of the graphene channel covered by self-induced top-gate electrode, *e* is electron charge,  $\mu$  is the mobility of the device, *n* is the carrier concentration induced in graphene channel by top-gate electrode, and  $n_0$  is the residual carrier concentration of graphene, which is generated by charged impurities<sup>25</sup> present in the graphene/ZnO microwire interface ( $n_0 = 2.45 \times 10^{11}$ cm<sup>-2</sup> for STG-FET device). The channel length is *L* and the width of the channel is *W*.

The extracted STG-FET device mobility ( $\mu$ ) based on the diffusive transport model state in eq 2 is exceeds 1630 cm<sup>2</sup>/(V s) for holes and 1240 cm<sup>2</sup>/(V s) for electrons. This present study shows that the ZnO microwire can be used as a top-gate electrode for G-FETs device without depositing any dielectric layer.

In summary, we have fabricated a graphene-FET device with ZnO microwire as a top-gate electrode. The depletion layer of the ZnO microwire is act as a gate dielectric for G-FETs with thickness of ~98 nm. The device characteristics are well agreed with the existing device models. The STG-FET device gives an on-current of 175  $\mu$ A, on/off current ratio of 55, and device mobility exceeding 1630 cm<sup>2</sup>/(V s) for holes and 1240 cm<sup>2</sup>/(V s) for electrons at room temperature. Self-induced gate dielectric process prevents the G-FETs from impurity doping, defect formation in graphene lattice and facilitates the fabrication process. The performance degradation of G-FETs can be overcome by our device structure.

#### ASSOCIATED CONTENT

#### **S** Supporting Information

The detailed synthesis process of ZnO microwire used for the fabrication of G-FET device is given along with a schematic diagram. This material is available free of charge via the Internet at http://pubs.acs.org/.

### AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: kimsangj@jejunu.ac.kr. Tel: +82-64-754-3715. Fax: +82-64-756-3886.

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This research work was supported by National Research Foundation of Korea Grant under Contract 2011-0015829.

#### REFERENCES

(1) Schwierz, F. Nat. Nanotechnol. 2010, 5, 487-496.

(2) Schedin, F.; Geim, A. K.; Morozov, S. V.; Hill, E. W.; Blake, P.; Katsnelson, M. I.; Novoselov, K. S. *Nat. Mater.* **2007**, *6*, 652–655.

(3) Novoselov, K. S.; Geim, A. K.; Morozov, S. V; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. *Science* **2004**, *306*, 666–669.

(4) Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Katsnelson, M. I.; Grigorieva, I. V.; Dubonos, S. V.; Firsov, A. A. *Nature* **2005**, *438*, 197–200.

(5) Zhang, Y. B.; Tan, Y. W.; Stormer, H. L.; Kim, P. Nature 2005, 438, 201–204.

(6) Tan, Y. W.; Zhang, Y.; Stormer, H. L.; Kim, P. Eur. Phys. J. Spec. Top. 2007, 148, 15–18.

(7) Morozov, S. V.; Novoselov, K. S.; Katsnelson, M. I.; Schedin, F.; Elias, D. C.; Jaszczak, J. A.; Geim, A. K. *Phys. Rev. Lett.* **2008**, *100*, 016602-1-016602-4.

(8) Hahnlein, B.; Handel, B.; Pezoldt, J.; Topfer, H.; Granzner, R.; Schwierz, F. *Appl. Phys. Lett.* **2012**, *101*, 093504–1–093504–3.

(9) Meric, I.; Han, M. Y.; Young, A. F.; Ozyilmaz, B.; Kim, P.; Shepard, K. Nat. Nanotechnol. 2008, 3, 654–659.

(10) Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. K. *Appl. Phys. Lett.* **2009**, *94*, 062107–1–062107–3.

(11) Liao, L.; Duan, X. Mater. Sci. Eng. R 2010, 70, 354-370.

(12) Liao, L.; Bai, J.; Lin, Y. C.; Qu, Y.; Huang, Y.; Duan, X. Adv. Mater. 2010, 22, 1941–1945.

(13) Lin, Y. M.; Chiu, H. Y.; Jenkins, K. A.; Farmer, D. B.; Avouris, P.; Valdes-Garcia, A. IEEE Electron Device Lett. **2010**, *31*, 68-70.

(14) Lemme, M. C.; Echtermeyer, T. J.; Baus, M.; Kurz, H. IEEE Electron Device Lett. 2007, 28, 282–284.

(15) Liao, L.; Lin, Y.-C.; Bao, M.; Cheng, R.; Bai, J.; Liu, Y.; Qu, Y.; Wang, K- L.; Huang, Yu.; Duan, X. *Nature* **2010**, *467*, 305–308.

(16) Liao, Z.-M.; Lv, Z.-K.; Zhou, Y.-B.; Xu, J.; Zhang, J.-M.; Yu, D.-P. Nanotechnology **2008**, *19*, 335204–1–335204–4.

(17) Kaschner, A.; Haboeck, U.; Strassburg, M.; Kaczmarzyk, G.; Hoffmann, A.; Thomsen, C.; Zeuner, A.; Alves, H. R.; Hofmann, D. M.; Meyer, B. K. *Appl. Phys. Lett.* **2002**, *80*, 1909–1911.

(18) Chai, G. Y.; Lupan, O.; Rusu, E. V.; Stratan, G. I.; Ursaki, V. V.;

Sontea, V.; Khallaf, H.; Chow, L. Sens. Actuators A 2012, 176, 64–71.

(19) Chai, G. Y.; Chowa, L.; Lupan, O.; Rusud, E.; Stratan, G. I.;

Heinrich, H.; Ursaki, V. V.; Tiginyanu, I. M. Solid State Sci. 2011, 13, 1205–1210.

(20) Liao, Z. M.; Zhang, H. Z.; Zhou, Y. B.; Xu, J.; Zhang, J. M.; Yu, D. P. *Phys. Lett. A* **2008**, *372*, 4505–4509.

(21) Vanheusden, K.; Warren, W. L.; Seager, C. H.; Tallant, D. R.; Voigt, J. A.; Gnade, B. E. J. Appl. Phys. **1996**, *79*, 7983–7990.

(22) Liao, Z. M.; Liu, K. J.; Zhang, J. M.; Xu, J.; Yu, D. P. *Phys.Lett. A* 2007, 367, 207–210.

(23) Liao, L.; Bai, J.; Qu, Y.; Lin, Y.-C.; Li, Y.; Huang, Y.; Duan, X. Proc. Natl. Acad. Sci. U.S.A **2010**, 107, 6711–6715.

(24) Wang, Y.; Huang, B.-C.; Zhang, M.; Miao, C.; Xie, Y.-H.; Woo, J. C. S. ISRN Electronics **2012**, 2012, 891480–1–891480–7.

(25) Adam, S.; Hwang, E. H.; Galitski, V. M.; Das Sarma, S. Proc. Natl. Acad. Sci. U.S.A 2007, 104, 18392–18397.